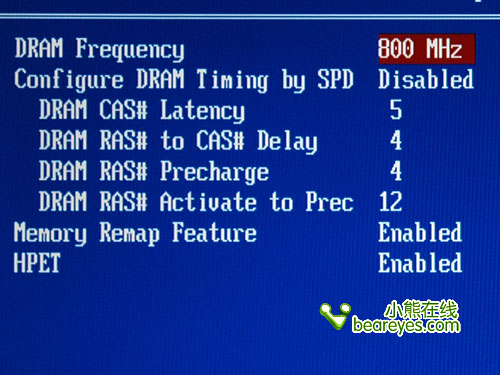

数字N分频就是采用N进制计数器实现功能。74HC393是双十六进制计数器,其QA、QB、QC和QD端分别是二、四、八和十六进制计数输出端。因此,直接将QC端引出即能得到f(cp)的八分之一。如图

怎样用74ls194 构成奇偶分频电路

用74161完成10分频是可以的,用一个二输入端与非门的两个输入端分别接到74161的输出端Qd和Qb,用与非门的输出作为74161的清零信号即可。

但是74161的输出方式和CD4017是不一样的,CD4017是由10个输出脚分别代表0~9,而74161是BCD码输出,如果要用74161改成的十进制计数器代替CD4017,还要加一个4-10译码器74HC42,而74HC42比CD4017还要贵些。

分频器低音电路中为什么并联一个电感和串联一个电

利用194来设计奇数或偶数型的计数器,可以用反馈移位的方法来设计,具体可以见西安电子科技大学出版社,杨颂华编的数字电子技术基础,第七章关于74LS194的部分 。设计时请注意能否自启动的问题。

分频器和计数器有本质联系,比如把输入信号作为模4计数器的时钟信号,那么计数器的输出就可以将输入信号4分频。

扩展资料:

第一,偶数倍分频:偶数倍分频应该是大家都比较熟悉的分频,通过计数器计数是完全可以实现的。如进行N倍偶数分频,那么可以通过由待分频的时钟触发计数器计数,当计数器从0计数到N/2‐1时,输出时钟进行翻转,并给计数器一个复位信号,使得下一个时钟从零开始计数。以此循环下去。这种方法可以实现任意的偶数分频。

第二,奇数倍分频:奇数倍分频有两种实现方法:

首先,完全可以通过计数器来实现,如进行三分频,通过待分频时钟上升沿触发计数器进行模三计数,当计数器计数到邻近值进行两次翻转,比如可以在计数器计数到1时,输出时钟进行翻转,计数到2时再次进行翻转。即是在计数值在邻近的1和2进行了两次翻转。

另外一种方法:对进行奇数倍n分频时钟,首先进行n/2分频(带小数,即等于(n‐1)/2+05),然后再进行二分频得到。得到占空比为50%的奇数倍分频。

-数字电路设计及Verilog HDL实现

分频器中的电感是为了选频,高音部分要滤掉低音信号,低音部分要滤掉高音信号,高音部分除了电感外还应串接一个电容才对,根据电感和电容组成的lc回路选择适当的频率。另外低音应该是串联电感,高音是并联电感后串联电容,我简单说一下原理,我尽量说的白话一点。

低音部分:电感对通过的电流有一个瞬间阻碍作用,就是它本身阻碍电流的变化,电流变化越快,它的阻碍作用越大,这就是所谓的感抗,串联到喇叭后,它就可以选频了,因为低音频率较低,阻碍作用较小,所以可以通过,高音频率高,也就是电流变化快,阻碍作用就大,于是高音部分被电感阻挡了无法通过,这就把低音信号从音源当中分离出来了。

高音部分:高音部分是并联一个电感,然后串联一个电容,道理一样,只不过反着用而已,低音信号从电感里通过,再通过电容匹配,已达到相位的平衡,音源功率损失很小。由于喇叭和电感是并联的,高音部分可以绕过电感的两端(就是喇叭)通过,由电容耦合。

这个是两分频电路,还有三分频电路,基本原理是一样的,只是在电路中中高音部分的电感可能被电阻所代替,不同的牌子和档次的分频器是不一样的,你说的这个属于功率型分频器,在高档功放中海使用电子分频器,用以选出信号后再进行功率放大,但是原理基本一致。