组合逻辑电路有:有编码器、译码器、数据选择器、加法器、数值比较器、函数发生器、奇偶校验器/发生器等。

组合逻辑电路的分析,是指对电路的状态变化过程进行分析,进而得出电路所要实现的功能。组合逻辑电路分析主要就是列出输入与输出的逻辑表达式并化简。一般步骤是根据逻辑图列出逻辑表达式,根据表达式列出正值表,对正值表进行运算化简,得到简化的逻辑表达式。

组合逻辑电路由与、或、非等逻辑门电路组成的。组合逻辑电路是指在任何时刻,输出状态只决定于同一时刻输入状态的组合,而与电路以前状态无关,而与其他时间的状态无关。

分析和设计用的方法不同,分析可以从逻辑图的入端往输出端写表达式,并化简,然后列真值表,分析逻辑功能;设计从真值表开始,由题目要求列真值表,写表达式,再化简画逻辑图。

组合逻辑电路由什么组成:

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。

组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。

基本逻辑门电路逻辑功能是什么?

一、组合逻辑电路的分析流程

与逻辑表示只有在决定事物结果的全部条件具备时,结果才发生。输出变量为1的某个组合的所有因子的与表示输出变量为1的这个组合出现、所有输出变量为0的组合均不出现,因而可以表示输出变量为1的这个组合。 组合逻辑电路的分析分以下几个步骤:

(1)有给定的逻辑电路图,写出输出端的逻辑表达式;

(2)列出真值表;

(3)通过真值表概括出逻辑功能,看原电路是不是最理想,若不是,则对其进行改进。

二、组合逻辑电路的设计步骤

(1) 由实际逻辑问题列出真值表;

(2) 由真值表写出逻辑表达式;

(3) 化简、变换输出逻辑表达式;

(4) 画出逻辑图。

扩展资料

常见的算术运算电路有:

1、半加器与全加器

①半加器

两个数A、B相加,只求本位之和,暂不管低位送来的进位数,称之为“半加”。

完成半加功能的逻辑电路叫半加器。实际作二进制加法时,两个加数一般都不会是一位,因而不考虑低位进位的半加器是不能解决问题的 。

②全加器

两数相加,不仅考虑本位之和,而且也考虑低位来的进位数,称为“全加”。实现这一功能的逻辑电路叫全加器。

2、加法器

实现多位二进制数相加的电路称为加法器。根据进位方式不同,有串行进位加法器和超前进位加法器两种 。

①四位串行加法器:如T692。优点:电路简单、连接方便。缺点:运算速度不高。最高位的计算,必须等到所有低位依此运算结束,送来进位信号之后才能进行。为了提高运算速度,可以采用超前进位方式 。

②超前进位加法器:所谓超前进位,就是在作加法运算时,各位数的进位信号由输入的二进制数直接产生。

-组合逻辑电路

逻辑电路的基本的逻辑电路——门电路

定义:

最基本的逻辑关系是与、或、非,最基本的逻辑门是与门、或门和非门。

实现“与”运算的叫 与门,实现“或”运算的叫 或门,实现“非”运算的叫非门,也叫做反相器,等等。

逻辑门是在集成电路(也称:集成电路)上的基本组件。

逻辑功能:

高、低电平可以分别代表逻辑上的“真”与“假”或二进制当中的1和0,从而实现逻辑运算。常见的逻辑门包括“与”门,“或”门,“非”门,“异或”门(也称:互斥或)等等。

逻辑门可以组合使用实现更为复杂的逻辑运算。

电路中的逻辑状态有哪些?什么是三态

简单的逻辑电路通常是由门电路构成,也可以用三极管来制作,例如,一个NPN三极管的集电极和另一个NPN三极管的发射极连接,这就可以看作是一个简单的与门电路,即:当两个三极管的基极都接高电平的时候,电路导通,而只要有一个不接高电平,电路就不导通。

常见的门电路如下所示:

非门:利用内部结构,使输入的电平变成相反的电平,高电平(1)变低电平(0),低电平(0)变高电平(1)。

A

B

0

1

1

0

与门:利用内部结构,使输入两个高电平(1),输出高电平(1),不满足有两个高电平(1)则输出低电平(0)。

A

B

C

0

0

0

0

1

0

1

0

0

1

1

1

或门:利用内部结构,使输入至少一个输入高电平(1),输出高电平(1),不满足有两个低电(0)输出高电平(1)

A

B

C

0

0

0

0

1

1

1

0

1

1

1

1

与非门:利用内部结构,使输入至多一个输入高电平(1),输出高电平(1),不满足有两个高电平(1)输出高电平(1)。

A

B

C

0

0

1

0

1

1

1

0

1

1

1

0

或非门:利用内部结构,使输入两个输入低电平(0),输出高电平(1),不满足有至少一个高电平(1)输出高电平(1)。

A

B

C

0

0

1

0

1

0

1

0

0

1

1

0

异或门:当输入端同时处于低电平(0)或高电平(1)时,输出端输出低电平(0),当输入端一个为高电平(1),另一个为低电平时(0),输出端输出高电平(1)。

A

B

C

0

0

0

0

1

1

1

0

1

1

1

0

同或门:当输入端同时输入低电平(0)或高电平(1)时,输出端输出高电平(1),当输入端一个为高电平(1),另一个为低电平时(0),输出端输出低电平(0)。

A

B

C

0

0

1

0

1

0

1

0

0

1

1

1

低电平输出 高电平输出 高阻态输出

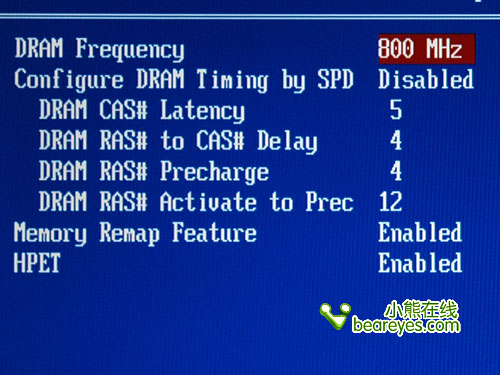

用逻辑电平来表示具体的电压信号值的一个大致范围,并且规定,电压范围在0~15V的电压信号称之为低电平,用数字0表示。电压范围在35V的电压信号称之为高电平,用数字1表示。还有一种状态,是在数字电路的总线应用的,叫做高组态所谓高阻态,指的是此时电路所处的状态既不是高电平也不是低电平,是一种不确定的状态有些总线传输,就应用这一点分时传输数据