不能工作。

开启电压大概是指数值上相等。 而且PMOS的VGS也是负的,当VGS的绝对值大于VTH的绝对值时,PMOS开始导通。低电平时PMOS的VGS的绝对值很大,NMOS的VGS的绝对值很小,所以pmos导通,NMOS截止。

PMOS接电源比较方便,出于功耗和速度的考量,所有的逻辑电路都是这样,比如NAND与非门。

没有必要使用PMOS和NMOS组成全桥整流电路,直接在电路输入中安装一只全桥整流桥不就可以得到整流电压了。

扩展资料:

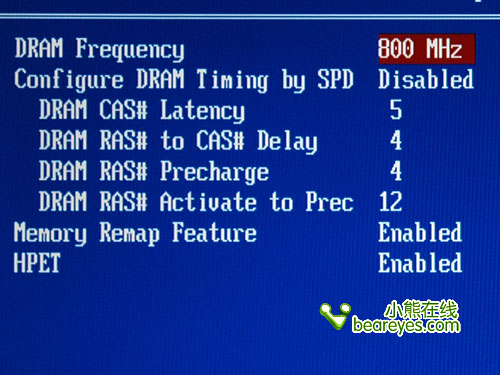

CMOS反相器电路由两个增强型MOS场效应管组成,其中V1为NMOS管,称驱动管,V2为PMOS管,称负载管。 NMOS管的栅源开启电压UTN为正值,PMOS管的栅源开启电压是负值,其数值范围在2~5V之间。为了使电路能正常工作,要求电源电压UDD>(UTN+|UTP|)。

UDD可在3~18V之间工作,其适用范围较宽。工作原理:当UI=UIL=0V时,UGS1=0,因此V1管截止,而此时|UGS2|>|UTP|,所以V2导通,且导通内阻很低,所以UO=UOH≈UDD, 即输出为高电平。当UI=UIH=UDD时,UGS1=UDD>UTN,V1导通,而UGS2=0<|UTP|,因此V2截止。

-反相器

关于一个电源电子开关的电路分析。用PNP和PMOS做的。

若经过测试确认,的确是IRF9540N的栅极电压不够,mos管的DS一直处于导通状态。那只能是IN4007,R7的电压分配与IRF9540N的VT不匹配导致。不行就把两个IN4007与R7去掉试试看。

还有一种情况,即使IRF9540N被关断,这个PMOS的drain端可能还会维持在一定程度的高电位,因为没有外力使得这个PMOS的drain端置零。

与非门的电路原理图是怎样的?

给你参考:

当5V存在时,Q1导通Q2截止,那么Q3截止,反之,Q1截止Q2导通,Q导通;

另外给个技巧点的方法(查了下Q3手册),只是担心Q3导通不够完全,你去试试吧;

在你原电路图中,发射极上再串联个电阻,如图,其他不变,目的是提升G点电压,使源栅电压小于夹断电压,从而使得控制端输入5V时,场效应管截止,输入0V时导通:

急求这个PMOS放大电路的增益推导过程

此电路功能为三输入与门形式,输入为A,B,C,输出为Y。用CMOS实现反相器电路,PMOS和NMOS管进行全互补连接方式,栅极相连作为输入,电路上面是三个PMOS并联,PMOS的漏极与下面NMOS的漏极相连作为输出,POMS管的源极和衬底相连接高电平,NMOS管的源极与衬底相连接低电平;

与非门是与门和非门的结合,先进行与运算,再进行非运算。与非门是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平。

原理图如下图所示

扩展资料:

与非门使用基本结构

1、首先考虑输入级,DTL是用二极管与门做输入级,速度较低。仔细分析发现电路中的Dl、D2、D3、D4的P区是相连的。可用集成工艺将它们做成一个多发射极三极管。这样它既是四个PN结,不改变原来的逻辑关系,又具有三极管的特性。

一旦满足了放大的外部条件,它就具有放大作用,为迅速消散T2饱和时的超量存储电荷提供足够大的反向基极电流,从而大大提高了关闭速度。

2、为提高输出管的开通速度,可将二极管D5改换成三极管T2,逻辑关系不变。同时在电路的开通过程中利用T2的放大作用,为输出管T3提供较大的基极电流,加速了输出管的导通。另外T2和电阻RC2、RE2组成的放大器有两个反相的输出端VC2和VE2,以产生两个互补的信号去驱动T3、T4组成的推拉式输出级。

3、再分析输出级。输出级应有较强的负载能力,为此将三极管的集电极负载电阻RC换成由三极管T4、二极管D和RC4组成的有源负载。由于T3和T4受两个互补信号Ve2和Vc2的驱动,所以在稳态时,它们总是一个导通,另一个截止。这种结构,称为推拉式输出级。

参考资料:

参考资料:

静态工作点要列方程组

UGS=Vdd-Uin

ID=IDSS(1-e^[UGS/Ugs(off)],(电流方程)

Uds=vcc-IDRD

交流等效电路

Au=-uo/ui=-IDRD/Ugs=-gmUgsRD/Ugs=-gmRD