当其为低电频时,计数器进行加计数,当其为高电频,时计数器进行减计数。计数是一种最简单基本的运算。计数器就是实现这种运算的逻辑电路。99-0减计数器工作原理是当其为低电频时,计数器进行加计数,当其为高电频,时计数器进行减计数。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,在运算器中作乘法、除法运算时记下加法、减法次数,又如在数字仪器中对脉冲的计数等等。

异步计数器(亦称波纹计数器,行波计数器):

组成异步计数器的触发器不是共用同一个时钟源,触发器的翻转不同时发生。

分类:计数器按计数脉冲的输入方式可分为:同步计数器和异步计数器。

实现方法:

1、同步计数器:实现是将计数脉冲引至所有的触发器的CP端,使应翻转的触发器能够同时的翻转;

2、异步计数器:实现是不将计数脉冲引至所有的触发器的CP端,而是将其它的触发器的输出引至其他的触发器的CP端,是不同时发生的。

特点:与同步计数器相比较,由于触发器不是共用同一个时钟源,触发器的翻转不能同时发生,所以工作速度慢。

扩展资料:

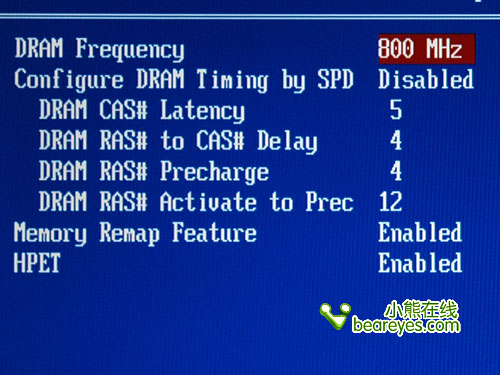

74ls74的工作原理:

SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。

设它们均已加入了高电平,不影响电路的工作。工作过程如下:

1、CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2、当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5=D,Q4=Q6=D。由基本RS触发器的逻辑功能可知,Q=D。

百度百科——74系列引脚图管脚图