组合逻辑电路的特点及设计时的注意事项:

①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中还要考虑器件和导线产生的延时)。

②组合逻辑电路设计时应尽量避免直接或间接的反馈,以免出现不确定的状态或形成振荡。如右图设计的基本触发器,当输入~S、~R从“00”变为“11”时,无法确定Q和~Q的值。

③组合逻辑电路容易出现“毛刺”,这是由于电路“竞争-冒险”产生的。如图所示,图中与门的两个输入分别由信号 A

经过不同路径传递而来。按照理想情况分 析,电路输出端应该始终为 L=A ·~A =0。考虑到信号在逻辑门中的传输延迟,~A

到达与门输入端的时间始终落后于 A。图(b)的波形显示,信号 A的四次变化都产生了竞争。但这四次竞争引起的结果是不一样的。第一次和第三次竞争造

成输出错误,第二次和第四次竞争则没有造成输出错误。换言之,只有第一次和第三次竞争引起了冒险,产生了尖峰干扰。

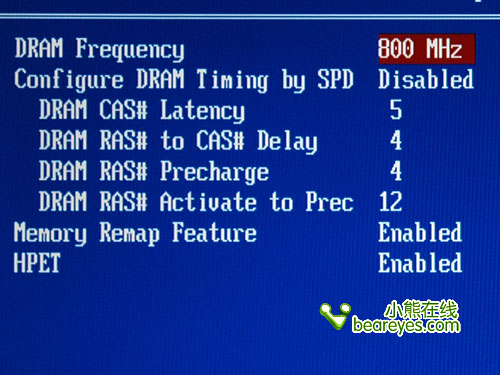

由于“毛刺”的影响,应避免使用组合逻辑电路直接产生时钟信号,也应避免将组合逻辑电路的输出作为另一个电路的异步控制信号。如右图,本意是设计一个计数范围为“0~5”的六进制计数器,即输出QD、QC、QB、QA从5“0101”变到6“0110”时,与门输出“1”,控制“CLR”异步复位到

“0000”,但是由于输出从3“0011”变到4“0100”时,QC先于QB从“0”变到“1”,导致短暂的“0111”出现,使与门输出“1”,引

起复位,从而使实际的电路计数范围为“0~3”,与设计的初衷相悖。

④用VHDL描述组合逻辑电路时,所有的输入信号都应放在敏感信号表中。

⑤用IF语句和CASE语句描述电路分支时,一定要列举出所有输入状态(一般在最后加上“else”或“when others”分支),否则在综合时将引入LATCH,使电路输出出现延时。

电路设计技巧盘点

电路装修是房屋装修的重要环节,新房装修电路注意事项是哪些?今日就由小编为你一一解答。

1、电路的设计需要将所有的可能性、可用性、可行性全部纳入考虑范围,而且还要做再三确认。其次,电路的灵活性也是一个很关键的影响因素。要知道将电器插头集中在一个插线板上的效果绝对比满墙的插座好。

2、如果要进行电路改造,那么线路的增容一定要参考实际的用电情况。如果是安装即热式的电热水器,那么电线必须是标准的4平方毫米。这样有效的避免在生活使用中出现短路的情况发生。

3、插座和地面的距离通常都是30厘米,不可以低于20厘米。如果安装的矮柜或是榻榻米的话,那么和地面的距离可以适当地调高一些。同时,矮柜和墙面要保持一点距离,否则很可能会挡住插座。

1、使用框图:本技巧似乎显而易见,但往往被过分自信的人忽视,他们认为自己已经把要做的活都弄明白了。完全按照你的需要表述电路的方框图对电路的成功设计至关重要。在你开始工作之前,方框图为你提供了一个大纲,它还为将要查看和检查你电路的任何人提供了极好的参考资料。

2、各个击破:在很多情况下,在设计电路时你可能不会单打独斗,所以花时间将设计划分为各功能块,每个块都有定义的接口,就可以实现各个击破的策略;参与电路设计的设计师可以专注于各个块。这些块可以独立地用于你目前正着手的项目,也可以在将来重复用于不同的电路设计。通过这种方法,你可以在事情不顺利的时候轻松排除故障,因为你将能够识别你遇到的麻烦是哪个块引起的。

3、为电路网络命名:的确,对这一步可能会有疑惑,但确保对pcb上的每个网络进行命名并标注每个网络的用途,可在紧要关头,为你提供诸多帮助。当你必须调试或运行模拟时,它也很有用。网络命名可让你在出问题时,知道该在哪下手。请记住:使命名易于识别;使命名对其要传载的意义一目了然。

4、记笔记:谈到电子设计,你的笔记就是你的灵丹妙药。重要的是记录研发过程的每一步,你遇到的每个坑、找到的每个解决方案、以及与你的设计相关的任何其它内容。请务必记下为什么为你的设计选用某些组件、逻辑表的式样、以及设计电路时的任何特殊注意事项。你的笔记有多种用途。

5、文本放置保持一致:如果你指定某些名称或在图表上进行注释,你会发现,再次查看时很难弄清这些文字到底是什么意思。在原理图上放置符号和名称时,请确保与命名过程保持一致。写注释时,不要在电路的一部分横着写,而在所有其它部分竖着写。尽量确保名称之间有一些空白,这样包括你在内的读者就不会感到困惑。注释间不要害怕有空白。实际上,空白有助于减少将图示与书写混在一起引发的混乱。这同样适用于速记命名。如果你要以缩写表述任何内容,请尝试在下面添加解释的“段子”,或确保它们易于识别。

6、流程化:不要削足适履试图将你的示意图(plan)和注释压缩进特定数量的页面。占页多少并不重要;不要苟且你原理图的质量。确保电路设计始终如一。这有助于提高可读性和更好的应用。在电子电路设计方面没有捷径;这完全取决于付出的努力和努力的结果。

7、保留标题:为原理图的每页制作标题、进而提供了每页的更多信息,这会使你受益。除可读性更高外,这样做还可以更轻松地为你的原理图页编制索引。这在调试时会带来益处:当你需要引用电路的某个部分、但又太忙无暇翻遍每一页、只得救助大脑记忆试图找出所需图表的位置时——页索引会帮大忙。

8、使连接器可见:你需要能立即区分所有连接器。最好的选择是在原理图中使用引脚表述连接器。通过简单的连接器识别,你将能够正确地追溯电路,且不会迷失在连接中。选用引脚之所以方便,是因为它将“坚守”其位置。与贴纸(sticker)或颜色不同,引脚能更突出引人注目,而不会在图表和笔记中占用太多空间。