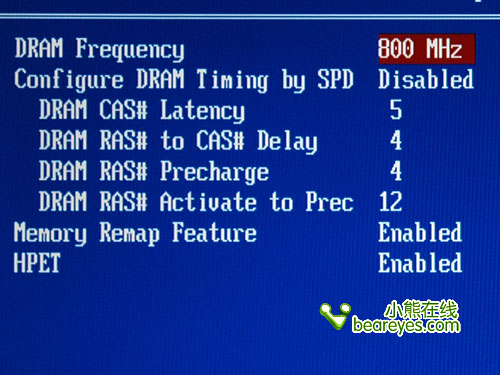

4LS161是4位2进制可预置同步计数器。

要做7进制计数,最大值是6(0110),数据端置0,取161输出6取反,去控制置数端(9脚),161会等到下一个时钟脉冲才置入数据,完成溢出归零控制。

用74161怎样设计一个十进制计数器电路???

计数器电路分频比通过计算器电路的输出频率与输入频率之比来确定。计数器电路的输出频率取决于其输入频率、计数器的位数和分频比等因素。分频比=2^N其中,N是计数器电路的位数。例如,如果一个4位二进制计数器被设计成进行16次计数,那么分频比就是2^4=16。这意味着输入信号的频率将被分频为原来的1/16。

数字电路怎样看是多少进制计数器

十进制数转换为二进制数时,由于整数和小数的转换方法不同,所以先将十进制数的整数部分和小数部分分别转换后,再加以合并。RCO =ET•QA•QB•QC•QD是进位输出端。

十进制整数转换为二进制整数 十进制整数转换为二进制整数采用"除2取余,逆序排列"法。具体做法是:

用2去除十进制整数,可以得到一个商和余数;再用2去除商,又会得到一个商和余数,如此进行,直到商为零时为止,然后把先得到的余数作为二进制数的低位有效位,后得到的余数作为二进制数的高位有效位,依次排列起来。

扩展资料:

所周知,计算机内部使用二进制表示数,二进制与十进制的转换是比较复杂的。比如要让计算机计算50+50,那么首先要把十进制的50转换成二进制的“50”——110010,这个过程要做多次除法,而计算机对于除法的计算是最慢的。

把十进制的50转换成二进制的110010还不算完,计算出结果1100100之后还要再转换成十进制数100,这是一个做乘法的过程,对计算机来说虽然比除法简单,但计算速度也不快。本来一步完成的事,却白白浪费了好多步骤,究其原因,就是人们使用的十进制不适应现代化信息设备,不是最佳信息计数法。

-十进制

数字电路计数器

先判断是同步计数器还是异步计数器:计数脉冲同时接到个触发器,各触发器状态的变换与计数脉冲同步即为同步计数器。

根据电路图写出逻辑表达式,再化简。根据表达式写出逻辑状态表。

最后根据逻辑状态表看是几进制计数器。比如逻辑状态表每过6个脉冲变化一次即为六进制计数器。

扩展资料:

逻辑电路的分析有以下四步:已知逻辑图写出逻辑表达式,利用逻辑代数化简或变换逻辑表达式,列出逻辑状态表,最后分析逻辑功能。

如何构成N进制计数器:利用反馈复位法,即当满足一定的条件时,利用计数器的复位端强迫计数器清零,重新开始新一轮计数。

利用反馈复位法可用已有的计数器得出小于原进制的计数器。

例如用一片T4290可构成十进制计数器,如将十进制计数器适当改接,利用其清零端进行反馈清零,则可以得出十以内的任意进制计数器。

数字电路的计数器设计?

用74ls161实现13进制计数器,清零法,就是在计到13时,产生复位信号而清零。

Q3Q2Q1Q0=1101,要用一个3输入的与非门产生复位信号。

仿真图如下,数码管是用来显示的,你可以省掉。最大数是12,即是C。

计数器是一种能够记录脉冲数目的装置,是数字电路中最常用的逻辑部件。计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数。

计数器按进位制不同,分为二进制计数器和十进制计数器;按运算功能不同,分为加法计数器、减法计数器和可逆计数器。下面我们以T触发器构成二进制加法、减法计数器为例介绍计数器的原理。

2计数器原理—加法计数器

用T触发器构成二进制加法计数器,如下图所示。

3位二进制加法器

如上图所示,是由3个下降沿触发的T触发器组成的3位二进制异步加法器,图中各个触发器的J、K输入端的输入信号均为1,主要由脉冲信号控制其输出信号,计数器从Q2 Q1 Q0 =000状态开始计数。

Q0、Q1、Q2的工作波形,如下图所示,即在计数输入脉冲CP的下降的触发下,触发器FF0的输出Q0要翻转。0变为1或1变为0。由于CP1取自Q0,所以在Q0的下降沿触发下,FF1的输出Q1要翻转。同理,由于CP2=Q1,所以在Q1的下降沿触发下,FF2的输出Q2要翻转。

若用上升沿触发的T′触发器同样可以组成异步二进制加法计数器,但每一级触发器的进位脉冲应改为Qˉ端输出。原因很简单,当低位触发器输出端Q端由1变为0时,Qˉ端的上升沿正好可以作为高位的触发脉冲。

3计数器原理—减法计数器

如果将T′触发器之间按二进制减法规则连接,就可以得到二进制减法计数器。根据二进制减法计数规则。若低位触发器已经为0,则再输入一个减法计数脉冲后应翻转为1,同时向高位发出借位信号,使高位翻转。

3位二进制减法器

上图就是按上述规则接成的3位二进制减法计数器。图中采用上升动作的D触发器接成的T′触发器,其中所有D触发器的D= Qˉ即成为T′触发器。它的时序图如下图所示